## Managing Complexity of Control Software through Concurrency

ISBN 90-365-2204-8

Printed by Ipskamp Enschede, the Netherlands

Cover design: Gerald Hilderink Cover art: Leny Bilderbeek-Wilens

© G.H. Hilderink, Enschede, 2005

No part of this work may be reproduced by print, photocopy, or any other means without the permission in writing from the publisher.

## MANAGING COMPLEXITY OF CONTROL SOFTWARE THROUGH CONCURRENCY

## PROEFSCHRIFT

ter verkrijging van de graad van doctor aan de Universiteit Twente, op gezag van de rector magnificus, prof. dr. W.H.M. Zijm, volgens besluit van het College voor Promoties in het openbaar te verdedigen op donderdag 19 mei 2005 om 15.00 uur

door

#### **Gerald Henk Hilderink**

geboren op 23 september 1968 te Haaksbergen Dit proefschrift is goedgekeurd door

Prof.dr.ir. J. van Amerongen

Dr.ir. J.F. Broenink

promotor

assistent-promotor

# Contents

| Vo | orw              | oord                                                          |                                          | ix |  |

|----|------------------|---------------------------------------------------------------|------------------------------------------|----|--|

| Su | ımm              | ary                                                           |                                          | xi |  |

| Sa | Samenvattingxiii |                                                               |                                          |    |  |

| 1  | Introduction     |                                                               |                                          |    |  |

|    | 1.1              | 1.1 Concurrency and complexities in embedded control software |                                          |    |  |

|    | 1.2              | Scope                                                         | of subject                               |    |  |

|    |                  | 1.2.1                                                         | Embedded control                         |    |  |

|    |                  | 1.2.2                                                         | Computer-aided design tools              | 6  |  |

|    |                  | 1.2.3                                                         | Multithreading                           | 7  |  |

|    |                  | 1.2.4                                                         | Occam and Transputer                     | 9  |  |

|    |                  | 1.2.5                                                         | THESIS                                   |    |  |

|    | 1.3              |                                                               |                                          |    |  |

|    | 1.4              |                                                               |                                          |    |  |

|    |                  | 1.4.1                                                         | Complexity                               |    |  |

|    |                  | 1.4.2                                                         | Concurrency                              |    |  |

|    |                  | 1.4.3                                                         | Communicating Sequential Processes       |    |  |

|    |                  | 1.4.4                                                         | Strategy                                 |    |  |

|    | 1.5              | Overv                                                         | view of thesis                           |    |  |

| 2  |                  |                                                               | red Approach to Embedded Control Systems | 23 |  |

|    | 2.1 Introduction |                                                               |                                          |    |  |

|   | 2.2                                                       | 2 Conceptual design for controller software of mechatronic systems     |                                                                                                                                                                                                     |                                                          |  |

|---|-----------------------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--|

|   |                                                           | 2.2.1                                                                  | Multidisciplinary design approach                                                                                                                                                                   | 25                                                       |  |

|   |                                                           | 2.2.2                                                                  | Control system design trajectory                                                                                                                                                                    | 27                                                       |  |

|   |                                                           | 2.2.3                                                                  | Stepwise refinement                                                                                                                                                                                 | 36                                                       |  |

|   | 2.3                                                       | Proces                                                                 | sses are in control                                                                                                                                                                                 | 38                                                       |  |

|   |                                                           | 2.3.1                                                                  | Processes                                                                                                                                                                                           | 38                                                       |  |

|   |                                                           | 2.3.2                                                                  | Identification of processes                                                                                                                                                                         | 39                                                       |  |

|   |                                                           | 2.3.3                                                                  | Process Analysis                                                                                                                                                                                    | 41                                                       |  |

|   |                                                           | 2.3.4                                                                  | Process Architecture Design                                                                                                                                                                         | 42                                                       |  |

|   | 2.4                                                       | The T                                                                  | HESIS method                                                                                                                                                                                        | 44                                                       |  |

|   | 2.5                                                       | Concl                                                                  | usions                                                                                                                                                                                              | 47                                                       |  |

| 3 |                                                           | phical Modelling Language for Specifying Concurrency                   |                                                                                                                                                                                                     |                                                          |  |

|   | bas                                                       | sed on CSP                                                             |                                                                                                                                                                                                     |                                                          |  |

|   |                                                           |                                                                        |                                                                                                                                                                                                     |                                                          |  |

|   | 3.1                                                       | Introd                                                                 | luction                                                                                                                                                                                             | 49                                                       |  |

|   | -                                                         |                                                                        | luction                                                                                                                                                                                             |                                                          |  |

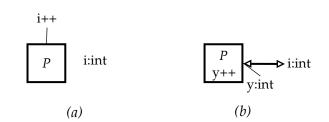

|   | 3.2                                                       | Proces                                                                 |                                                                                                                                                                                                     | 51                                                       |  |

|   | <ul><li>3.2</li><li>3.3</li></ul>                         | Proces<br>The C                                                        | sses and objects                                                                                                                                                                                    | 51<br>53                                                 |  |

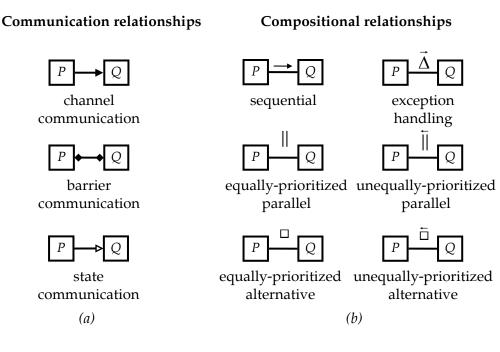

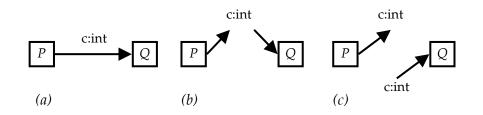

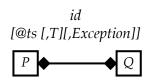

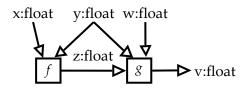

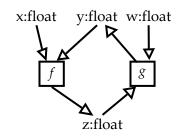

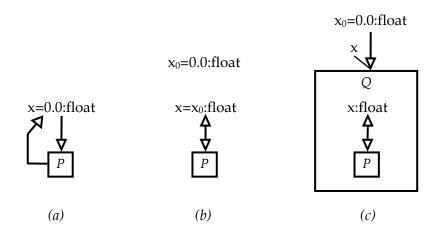

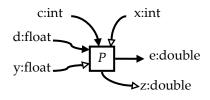

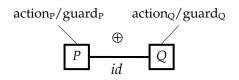

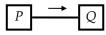

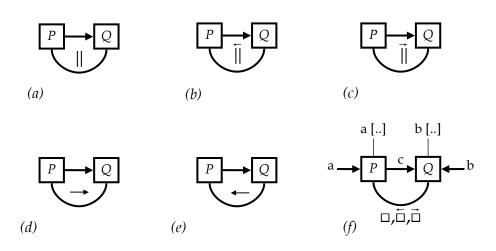

|   | <ul><li>3.2</li><li>3.3</li><li>3.4</li></ul>             | Proces<br>The C<br>Interre                                             | sses and objects<br>SP diagram                                                                                                                                                                      | 51<br>53<br>56                                           |  |

|   | <ul><li>3.2</li><li>3.3</li><li>3.4</li></ul>             | Proces<br>The C<br>Interre                                             | sses and objects<br>SP diagram<br>elationships                                                                                                                                                      | 51<br>53<br>56<br>58                                     |  |

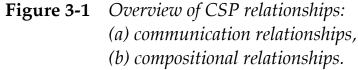

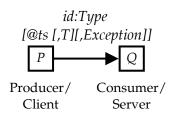

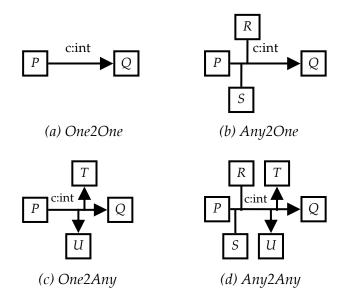

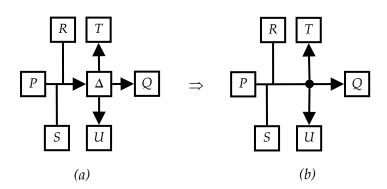

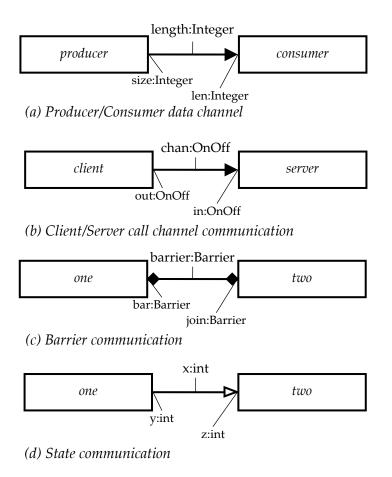

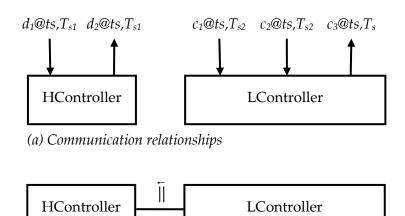

|   | <ul><li>3.2</li><li>3.3</li><li>3.4</li></ul>             | Proces<br>The C<br>Interro<br>Comm                                     | sses and objects<br>SP diagram<br>elationships<br>nunication relationships                                                                                                                          | 51<br>53<br>56<br>58<br>59                               |  |

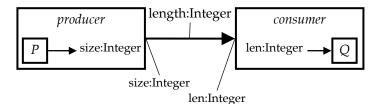

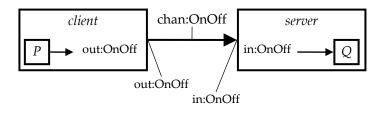

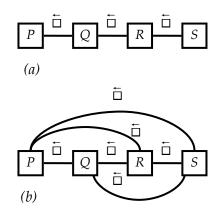

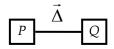

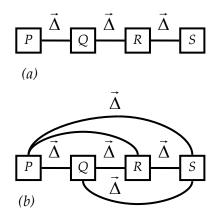

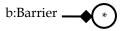

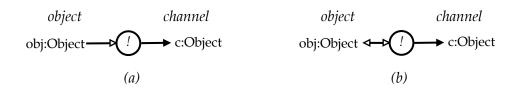

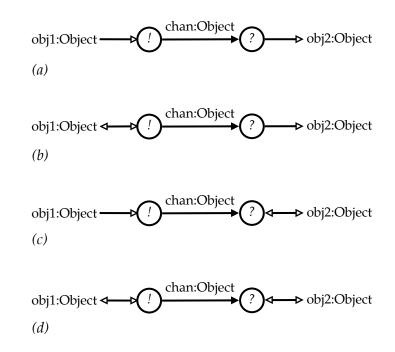

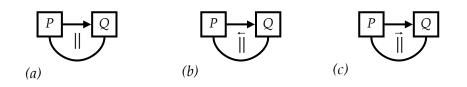

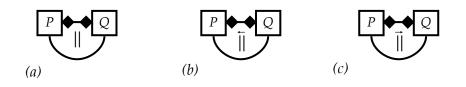

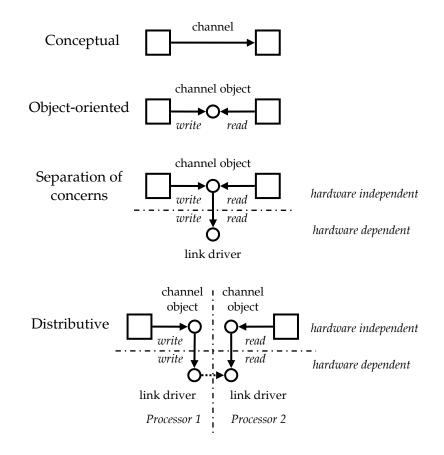

|   | <ul><li>3.2</li><li>3.3</li><li>3.4</li></ul>             | Proces<br>The C<br>Interro<br>Comm<br>3.5.1                            | sses and objects<br>SP diagram<br>elationships<br>nunication relationships<br>Channel communication                                                                                                 | 51<br>53<br>56<br>58<br>59<br>65                         |  |

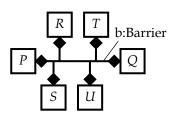

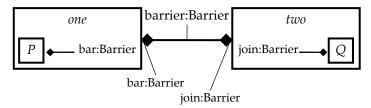

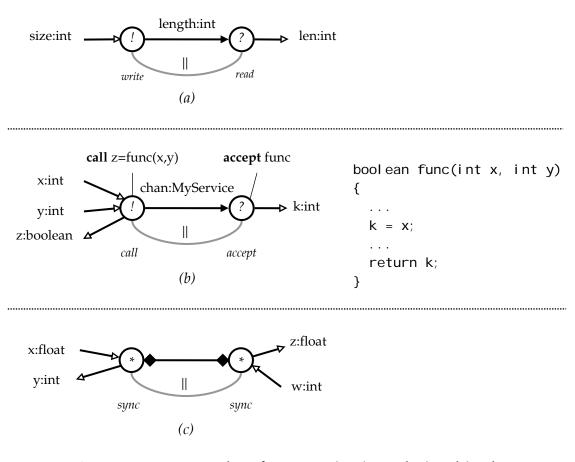

|   | <ul><li>3.2</li><li>3.3</li><li>3.4</li></ul>             | Proces<br>The C<br>Interro<br>Comm<br>3.5.1<br>3.5.2                   | sses and objects<br>SP diagram<br>elationships<br>nunication relationships<br>Channel communication<br>Barrier communication                                                                        | 51<br>53<br>56<br>58<br>59<br>65<br>66                   |  |

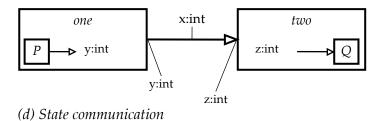

|   | <ul><li>3.2</li><li>3.3</li><li>3.4</li></ul>             | Proces<br>The C<br>Interro<br>3.5.1<br>3.5.2<br>3.5.3<br>3.5.4         | sses and objects<br>SP diagram<br>elationships<br>nunication relationships<br>Channel communication<br>Barrier communication<br>State Communication                                                 | 51<br>53<br>56<br>58<br>59<br>65<br>66<br>71             |  |

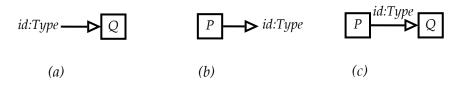

|   | <ul><li>3.2</li><li>3.3</li><li>3.4</li><li>3.5</li></ul> | Proces<br>The C<br>Interro<br>3.5.1<br>3.5.2<br>3.5.3<br>3.5.4         | Sees and objects<br>SP diagram<br>elationships<br>nunication relationships<br>Channel communication<br>Barrier communication<br>State Communication<br>Process interface                            | 51<br>53<br>56<br>58<br>59<br>65<br>66<br>71<br>75       |  |

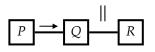

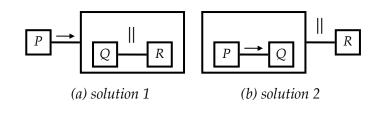

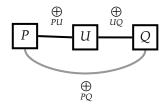

|   | <ul><li>3.2</li><li>3.3</li><li>3.4</li><li>3.5</li></ul> | Proces<br>The C<br>Interro<br>3.5.1<br>3.5.2<br>3.5.3<br>3.5.4<br>Comp | sses and objects<br>SP diagram<br>elationships<br>nunication relationships<br>Channel communication<br>Barrier communication<br>State Communication<br>Process interface<br>ositional relationships | 51<br>53<br>56<br>58<br>59<br>65<br>66<br>71<br>75<br>76 |  |

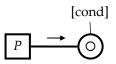

|   |      | 3.6.4  | Alternative relationships                           |     |

|---|------|--------|-----------------------------------------------------|-----|

|   |      | 3.6.5  | Exception relationships                             |     |

|   |      | 3.6.6  | Anonymous repetitions                               |     |

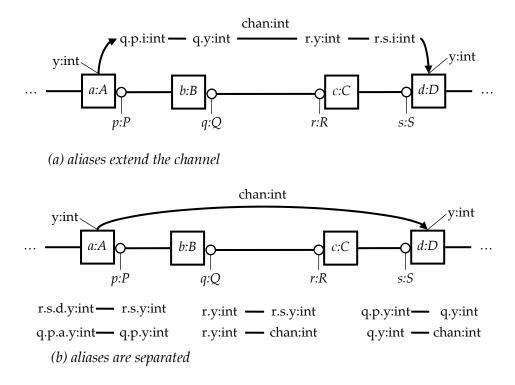

|   |      | 3.6.7  | Aliases                                             |     |

|   |      | 3.6.8  | Primitive communication processes                   |     |

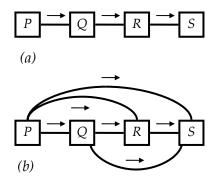

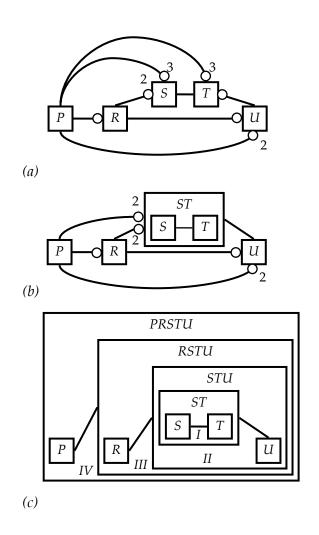

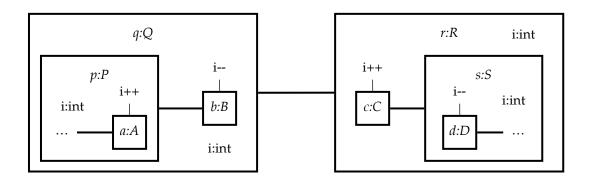

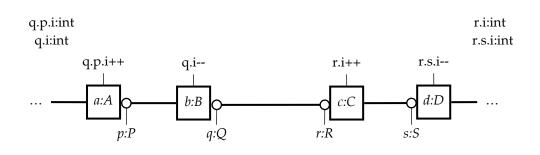

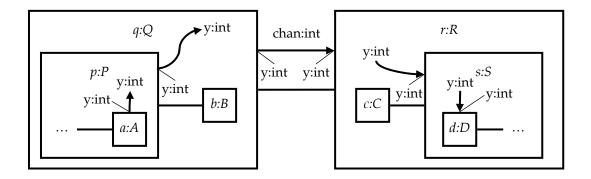

|   | 3.7  | Hieran | rchies                                              | 102 |

|   |      | 3.7.1  | Ambiguity and Unambiguity                           | 102 |

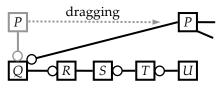

|   |      | 3.7.2  | Indexed parenthesizing relationships                | 105 |

|   |      | 3.7.3  | Compositional undefined relationships               | 106 |

|   |      | 3.7.4  | Deep hierarchies versus flat hierarchies            | 107 |

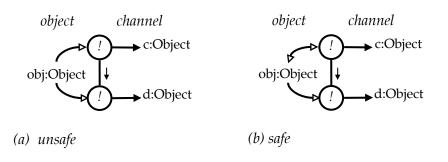

|   | 3.8  | Analy  | sis techniques and rules                            | 113 |

|   |      | 3.8.1  | State communication rules                           | 113 |

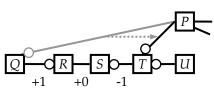

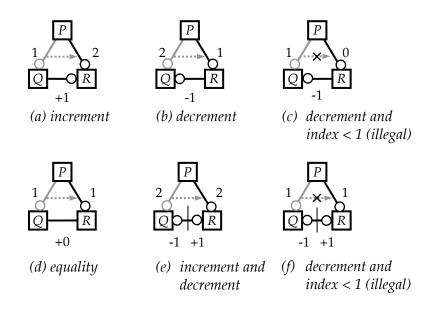

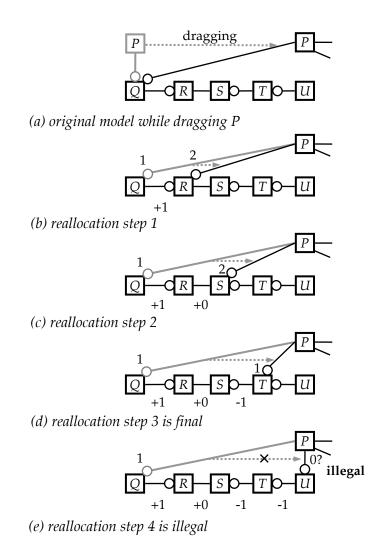

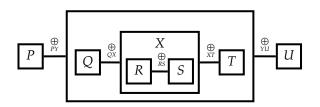

|   |      | 3.8.2  | Reallocation rules                                  | 114 |

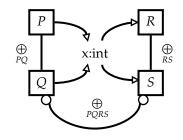

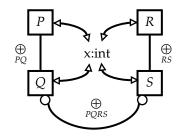

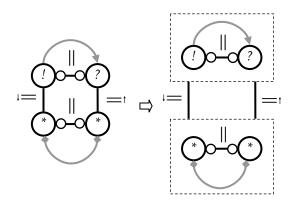

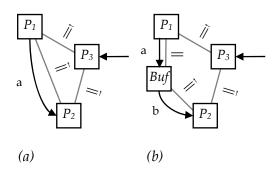

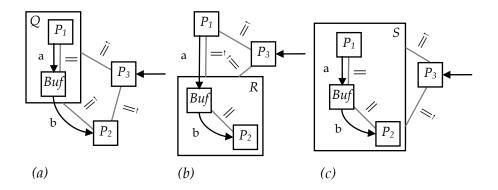

|   |      | 3.8.3  | Balanced and unbalanced parenthesized cycles        | 118 |

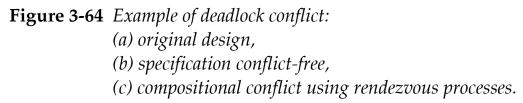

|   |      | 3.8.4  | Compositional conflicts                             | 120 |

|   |      | 3.8.5  | Companionship between communication and composition | 125 |

|   | 3.9  | Desig  | n freedom                                           | 127 |

|   | 3.10 | Refine | ement and verification                              | 128 |

|   | 3.11 | Conclu | usions                                              | 129 |

| 4 |      |        | rary for compositional programming of concurren     |     |

|   | soft | ware   |                                                     | 133 |

|   | 4.1  | Introd | luction                                             | 133 |

|   | 4.2  | Appro  | oach and background                                 | 134 |

|   |      | 4.2.1  | CT object model                                     | 134 |

|   |      | 4.2.2  | Java thread model                                   | 135 |

|   |      | 4.2.3  | Communicating Threads for Java                      | 136 |

|                         | 4.2.4            | Aspects                          | 136 |  |  |

|-------------------------|------------------|----------------------------------|-----|--|--|

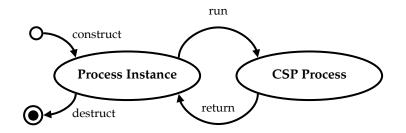

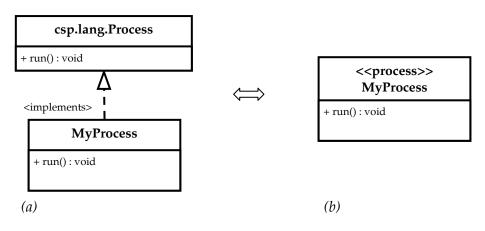

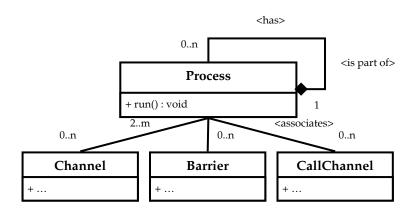

| 4.3                     | Processes        |                                  |     |  |  |

|                         | 4.3.1            | Process instance interface       | 140 |  |  |

|                         | 4.3.2            | Process communication interface  | 142 |  |  |

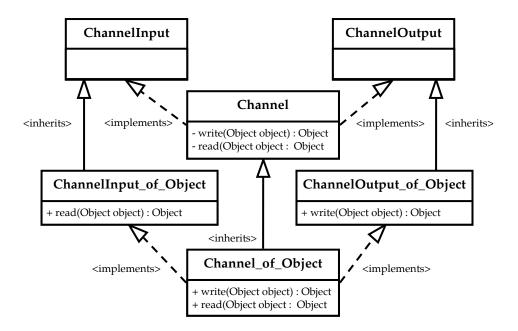

| 4.4                     | Chanr            | nels                             | 143 |  |  |

|                         | 4.4.1            | Synchronization                  | 143 |  |  |

|                         | 4.4.2            | Scheduling                       | 144 |  |  |

|                         | 4.4.3            | Message delivery                 | 144 |  |  |

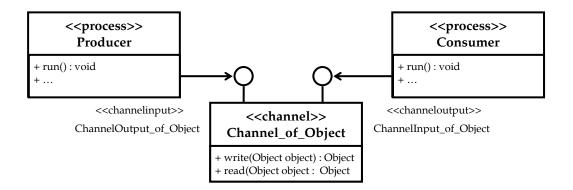

|                         | 4.4.4            | Data channels                    | 145 |  |  |

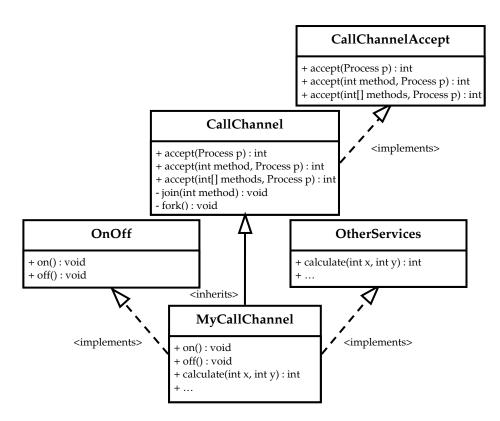

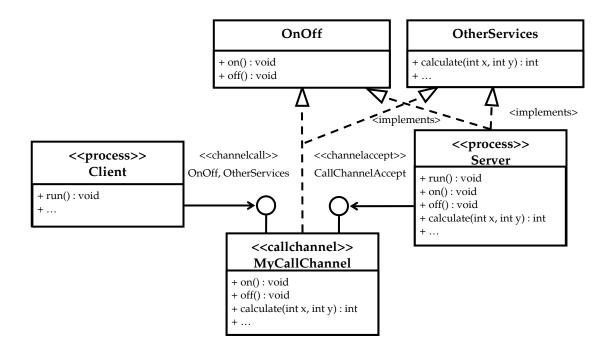

|                         | 4.4.5            | Call channels                    | 154 |  |  |

| 4.5                     | Barrie           | Prs                              | 156 |  |  |

| 4.6                     | Comp             | oositional constructs            | 158 |  |  |

|                         | 4.6.1            | The parallel construct           | 159 |  |  |

|                         | 4.6.2            | The sequential construct         | 163 |  |  |

|                         | 4.6.3            | The alternative construct        | 164 |  |  |

|                         | 4.6.4            | The exception handling construct | 171 |  |  |

|                         | 4.6.5            | Nested compositional constructs  | 178 |  |  |

| 4.7                     | Timin            | ng and Sampling                  | 179 |  |  |

|                         | 4.7.1            | Timed communication events       | 180 |  |  |

|                         | 4.7.2            | System services                  | 181 |  |  |

|                         | 4.7.3            | Thread services                  | 184 |  |  |

|                         | 4.7.4            | Example real-time timing         | 185 |  |  |

| 4.8                     | Concl            | usions                           | 191 |  |  |

| Notion of priorities193 |                  |                                  |     |  |  |

| 5.1                     | 5.1 Introduction |                                  |     |  |  |

| 5.2                     | Priori           | ty relationship                  | 194 |  |  |

|                         | <b>y i</b>       |                                  |     |  |  |

5

#### Contents

|   | 5.3 | Equall                         | y- and unequally-prioritized parallel constructs | . 196 |

|---|-----|--------------------------------|--------------------------------------------------|-------|

|   | 5.4 | The priority inversion problem |                                                  |       |

|   | 5.5 | Sched                          | uling of communication primitives                | . 203 |

|   |     | 5.5.1                          | Scheduling of data channels                      | . 203 |

|   |     | 5.5.2                          | Scheduling of call channels                      | . 205 |

|   |     | 5.5.3                          | Scheduling of barriers                           | . 207 |

|   | 5.6 | Alting                         | with notion of priority                          | . 208 |

|   |     | 5.6.1                          | Resolute alting versus preference alting         | . 209 |

|   |     | 5.6.2                          | Preference alting implementation                 | . 213 |

|   | 5.7 | Efficie                        | ncy                                              | . 215 |

|   |     | 5.7.1                          | Waiting queues                                   | . 215 |

|   |     | 5.7.2                          | Ready queues                                     | . 216 |

|   |     | 5.7.3                          | Alting queues                                    | . 216 |

|   | 5.8 | Outpu                          | ıt guards                                        | . 217 |

|   |     | 5.8.1                          | Alting disagreement                              | . 218 |

|   |     | 5.8.2                          | Alting agreement                                 | . 221 |

|   |     | 5.8.3                          | Model checking and priorities                    | . 222 |

|   | 5.9 | Conclu                         | usions                                           | . 222 |

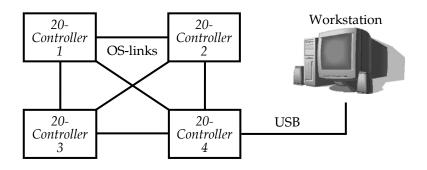

| 6 | CSI | conce                          | pts applied to control systems                   | . 225 |

|   | 6.1 | Introd                         | uction                                           | . 225 |

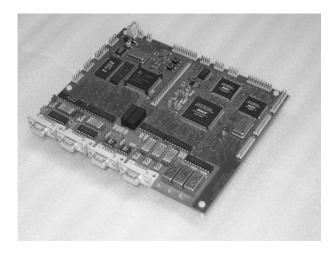

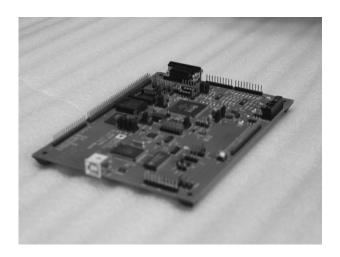

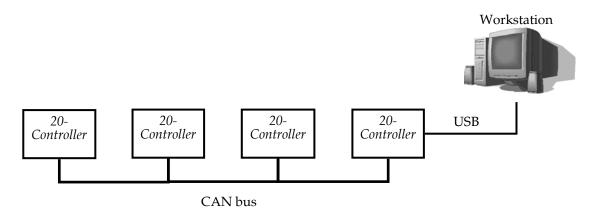

|   | 6.2 | 20-Coi                         | ntroller                                         | . 225 |

|   | 6.3 | MIMC                           | 0-OFDM test bed                                  | . 229 |

|   | 6.4 | Labora                         | atory PC and embedded PC                         | . 229 |

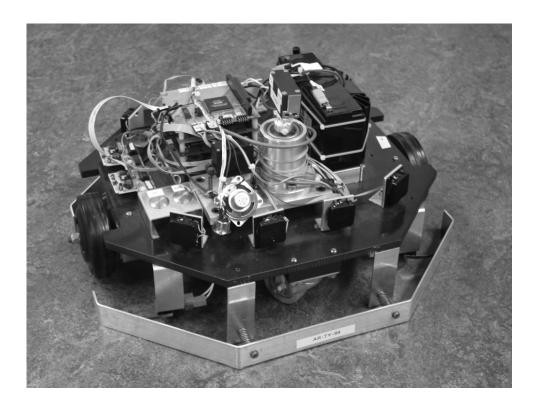

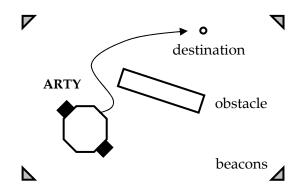

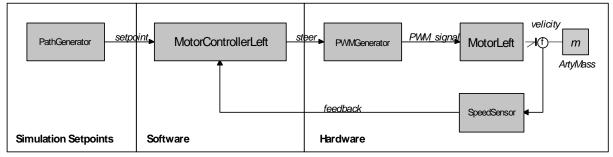

|   | 6.5 | ARTY                           | , an autonomous robot                            | . 230 |

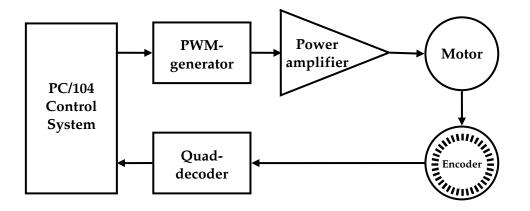

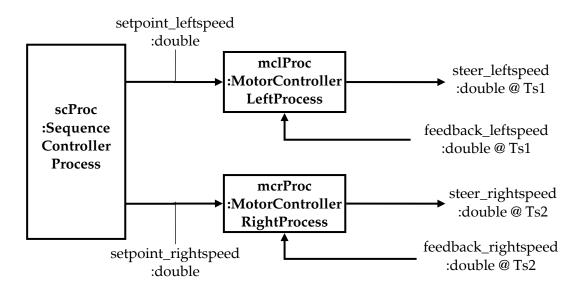

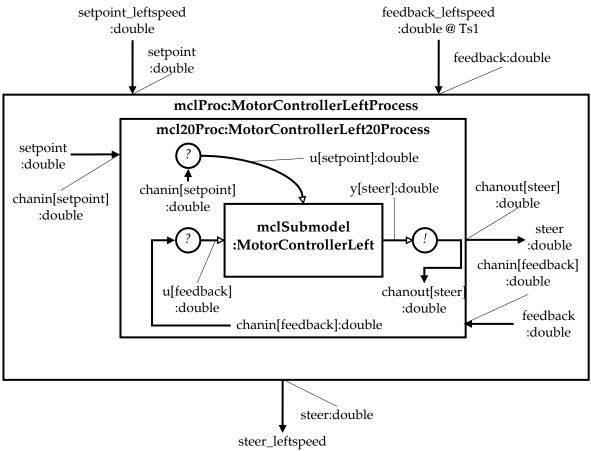

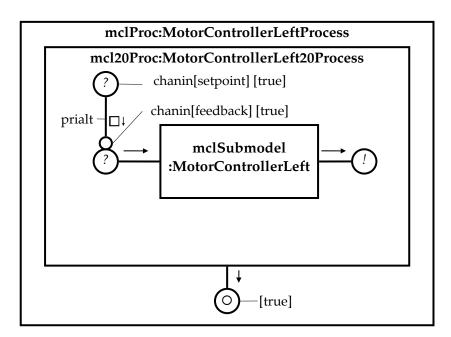

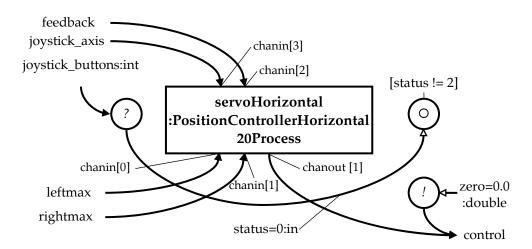

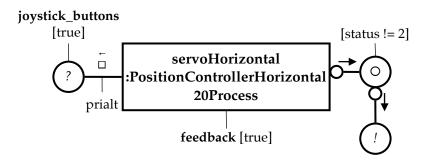

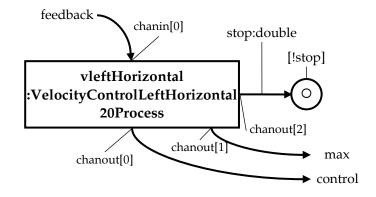

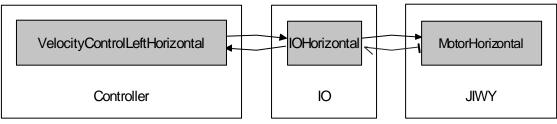

|   |     | 6.5.1                          | Motor controller description                     | . 233 |

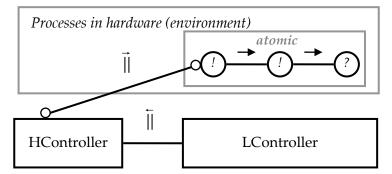

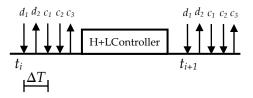

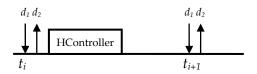

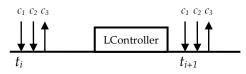

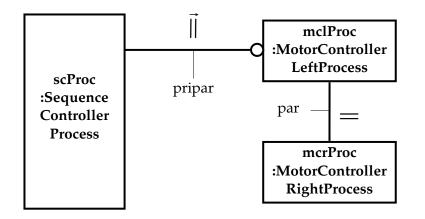

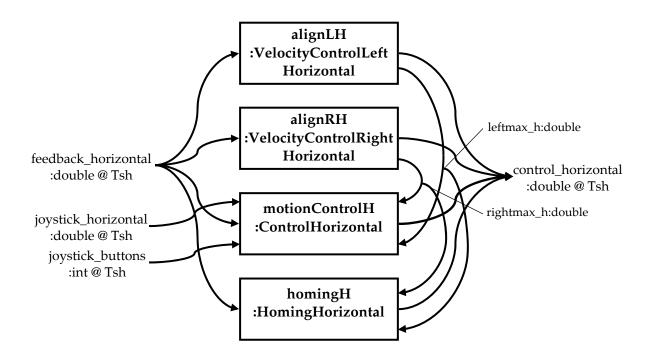

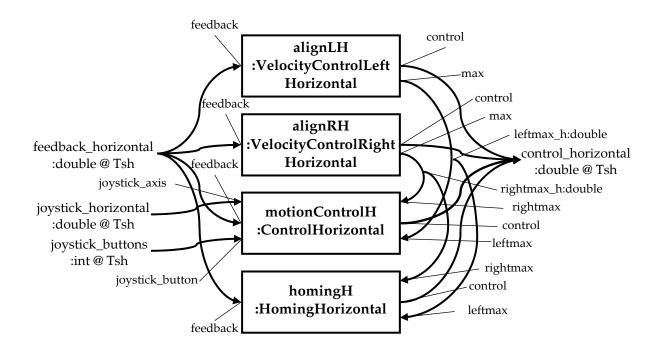

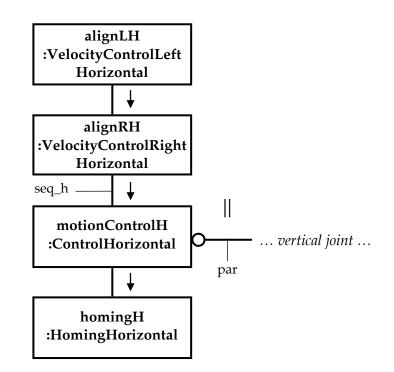

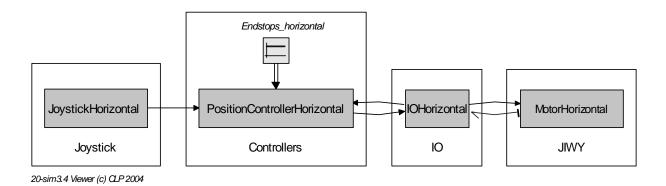

|   |     | 6.5.2                          | Process architecture                             | . 234 |

| 0.40  |

|-------|

|       |

|       |

|       |

|       |

|       |

|       |

|       |

|       |

|       |

|       |

|       |

|       |

|       |

|       |

|       |

|       |

|       |

| P 279 |

|       |

|       |

|       |

|       |

|       |

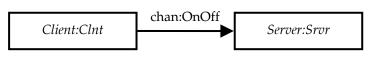

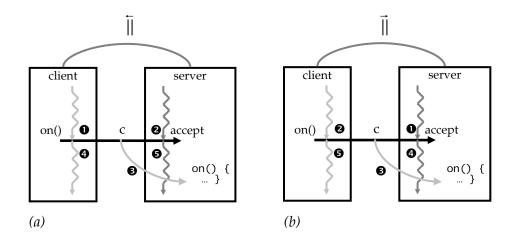

|   | D.2 | D.2 Client/Server example |                                           |     |  |

|---|-----|---------------------------|-------------------------------------------|-----|--|

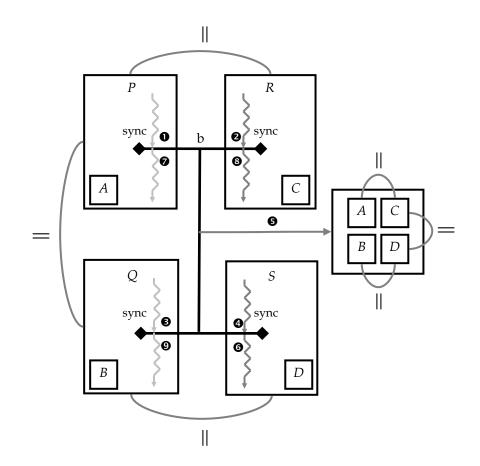

|   | D.3 | 0.3 Barrier Example       |                                           |     |  |

|   | D.4 | 0.4 Additional Guards     |                                           |     |  |

|   |     | D.4.1                     | Skip guards                               | 298 |  |

|   |     | D.4.2                     | Timeout guards                            | 299 |  |

|   | D.5 | State h                   | nandling methods                          | 300 |  |

|   | D.6 | ARTY                      | Implementation                            | 301 |  |

|   |     | D.6.1                     | Top network builder                       | 301 |  |

|   |     | D.6.2                     | MotorControllerLeftProcess                | 303 |  |

|   |     | D.6.3                     | MotorControllerLeft20Process              | 304 |  |

|   | D.7 | JIWY                      | Implementation                            | 305 |  |

|   |     | D.7.1                     | Top network builder                       | 305 |  |

|   |     | D.7.2                     | Motion controller process                 | 309 |  |

|   |     | D.7.3                     | Alignment controller process              | 310 |  |

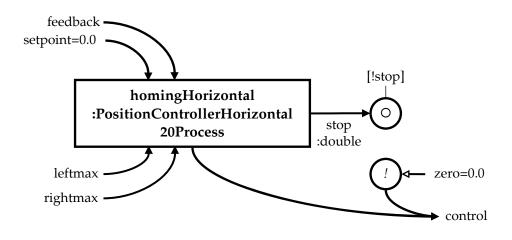

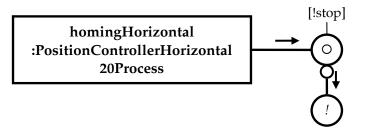

|   |     | D.7.4                     | Homing controller process                 | 312 |  |

| Ε | Alt | ing                       |                                           | 315 |  |

|   | E.1 | Introd                    | luction                                   | 315 |  |

|   | E.2 | Fair al                   | lting                                     | 315 |  |

|   | E.3 | Any-to                    | o-any channel                             | 316 |  |

|   | E.4 | Semar                     | ntics of alting                           | 321 |  |

|   | E.5 | Prope                     | rties of alting                           | 324 |  |

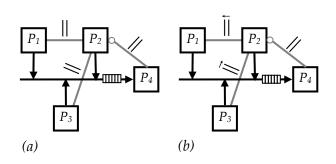

| F | Sol | ving pr                   | riority conflicts with buffered channels  | 327 |  |

|   | F.1 | Introd                    | luction                                   | 327 |  |

|   | F.2 | Buffer                    | ed data channels solve priority conflicts | 328 |  |

| G |     |                           | ional analysis rule                       |     |  |

|   |     | ±                         |                                           |     |  |

|    | G.1 Introduction                         | . 331 |  |  |  |

|----|------------------------------------------|-------|--|--|--|

|    | G.2 Triangular cycles                    | . 331 |  |  |  |

|    | G.3 Compositional Analysis Rule          | . 333 |  |  |  |

| н  | Pass-by-reference versus pass-by-value   | . 335 |  |  |  |

|    | H.1 Pass-by-reference                    | . 335 |  |  |  |

|    | H.2 Pass-by-value                        | . 336 |  |  |  |

|    | H.3 Message passing for control software | . 337 |  |  |  |

| N  | otation                                  | . 339 |  |  |  |

| Bi | Bibliography                             |       |  |  |  |

| Cı | Curriculum vitae                         |       |  |  |  |

# Voorwoord

In traditionele methoden, zoals ik die gedurende mijn opleidingen kreeg voorgeschoteld, heb ik tekortkomingen en valkuilen ervaren bij het ontwikkelen van software voor ingebedde systemen. Bepaalde ontwikkelingen op het gebied van software ontwerpen en programmeren maakten de dingen complexer in plaats van juist eenvoudiger. Door het bestuderen van de programmeertaal occam en de achterliggende theoretische concepten, heb ik ontdekt dat er wel een paradigma bestaat dat software simpeler maakt in plaats van complexer. De clou zat hem in een elegante benaderen van 'concurrency'.

Ik had het geluk dat mijn ideeën, in het kader van mijn afstudeeronderzoek, resulteerden in dit promotieonderzoek bij de Leerstoel Regeltechniek van de Faculteit Elektrotechniek, Wiskunde en Informatica (EWI) aan de Universiteit Twente. Door dit onderzoek heb ik geleerd om software voor ingebedde systemen op een adequate en systematische manier aan te pakken, d.w.z. dat concurrency de complexiteit in de hand houdt. Door deelname aan conferenties en reacties op eerdere publicaties heb ik kunnen vaststellen dat mijn bevindingen ook ervaren en gedeeld worden door anderen.

Graag wil ik Job van Amerongen, Jan Broenink en André Bakkers bedanken dat zij dit onderzoek mogelijk hebben gemaakt. Dusko Jovanovic, Bojan Orlic en Peter Visser wil ik bedanken voor alle suggesties en discussies die ik met hen gehad heb. Natuurlijk ben ik ook mijn dank verschuldigd aan die talloze studenten die hun bijdrage hebben geleverd aan dit onderzoek. Mijn stiefvader Jan Bilderbeek en mijn moeder wil ik van harte bedanken voor hun steun en adviezen, en mijn moeder vooral voor haar creativiteit gelegd in de omslag van mijn proefschrift. En dan nu wil ik mijn lieve José bedanken voor haar geduld, toeverlaat en liefde gedurende dit karwei. Dankjewel lieve mensen!

Gerald Hilderink

Enschede, 16 april 2005.

# Summary

In this thesis, we are concerned with the development of concurrent software for embedded systems. The emphasis is on the development of control software.

Embedded systems are concurrent systems whereby hardware and software communicate with the concurrent world. Concurrency is essential, which cannot be ignored. It requires a proper handling to avoid pathological problems (e.g. deadlock and livelock) and performance penalties (e.g. starvation and priority conflicts). Multithreading, as such, leads to sources of complexity in concurrent software. This complexity is considered frightening, because it complicates the software designs and code. Moreover, this the resulting paradigm complicates the understanding of the behaviour of concurrent software.

A paradigm with a precise understanding of concurrency is essential. In this thesis, a methodology is proposed that comprises a paradigm of fundamental aspects of concurrency. These fundamental aspects are derived from the *Communicating Sequential Processes* (CSP) theory. CSP is a theory of programming that is developed by Hoare, Brookes, and Roscoe. CSP comprises *fundamental concepts* useful for precisely describing and studying concurrent systems. These concepts are based on processes and events. Processes and events are abstract entities, more abstract than objects. Processes and events are essential in describing and reasoning about the real-time behaviour of process architectures. A process architecture describes a (sub-) program as a composition of communicating processes.

The proposed methodology brings a subset of CSP to practice in order to specify, design, and implement process architectures. The CSP concepts bring forth a glue-logic between these phases in the development trajectory. Furthermore, these concepts offer technical solutions, which have been enhanced with notion of priorities, exception handling, and timing. The precise semantics of the concepts and their restrictions provide the guidelines to create reliable and robust concurrent software. The abstraction and separation of well-defined concerns contribute to managing complexity in concurrent software.

The proposed methodology defines the following ingredients:

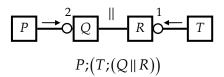

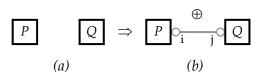

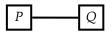

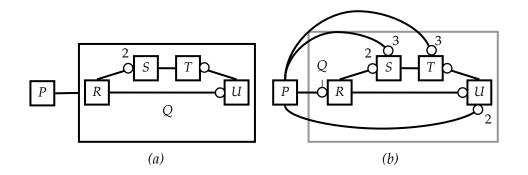

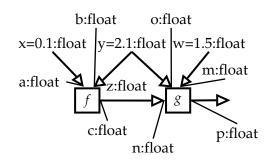

- 1. A *graphical modelling language* defines graphical notations and rules that are derived from CSP. The graphical modelling language is used for specifying, designing, and graphically programming process architectures. This results in *CSP diagrams*.

- 2. An *object model* implements the CSP concepts by means of objectoriented techniques. This model can be implemented in objectoriented programming languages. This results in the *CSP libraries* for Java, C (in object-oriented style) and C++.

The graphical modelling language and the object model go together. CSP diagrams are used to describe and to analyse process architectures. A CSP library is used to implement process architectures in an object-oriented programming language. This methodology uses process-oriented and object-oriented techniques, and hides thread-oriented techniques.

The proposed methodology is applied to control applications on embedded computer systems.

# Samenvatting

In dit proefschrift houden we ons bezig met de ontwikkeling van concurrent software voor ingebedde systemen. De nadruk ligt op de ontwikkeling van regelsoftware.

Ingebedde systemen zijn concurrent systemen, waarbij hardware en software communiceren met de concurrent wereld. Concurrency is wezenlijk en kan niet worden genegeerd. Het vereist een goede behandeling die pathologische problemen (zoals deadlock en livelock) en prestatieproblemen (zoals starvation en prioriteitconflicten) dienen te voorkomen. Multihreading, als zodanig, leidt tot een bron van complexiteit in concurrent software. Deze complexiteit wordt als afschrikwekkend ervaren, want het bemoeilijkt de softwareontwerpen en de resulterende code. Bovendien bemoeilijkt dit paradigma het begrijpen van het gedrag van concurrent software.

Een paradigma met een precieze kennis van concurrency is essentieel. In dit proefschrift wordt een methodologie voorgesteld dat een paradigma van fundamentele concurrency aspecten behelst. Deze fundamentele aspecten zijn ontleend aan de Communicating Sequential Processes (CSP) theorie. CSP is een theorie over programmeren die is ontwikkeld door Hoare, Brookes en Roscoe. CSP behelst fundamentele concepten die geschikt zijn voor het nauwkeurig bestuderen van concurrent systemen. Deze concepten zijn gebaseerd op processen en events. Processen en events zijn abstracte entiteiten, abstracter dan objecten. Processen en events zijn noodzakelijk voor het beschrijven van en het redeneren over het real-time gedrag van procesarchitecturen. Een procesarchitectuur (deel-) programma beschrijft een als een samenstelling van communicerende processen.

De voorgestelde methodologie brengt een deelverzameling van de CSP theorie naar de praktijk voor het specificeren, ontwerpen en implementeren van proces architecturen. Deze CSP concepten leiden tot een perfecte passing van deze fasen in het ontwikkeltraject. Bovendien bieden deze concepten technische oplossingen, welke zijn aangevuld met prioriteiten, foutenafhandeling en notie van tijd. De precieze betekenissen van de concepten en hun beperkingen zorgen voor richtlijnen om betrouwbare en robuuste ingebedde regelsoftware te ontwikkelen. De abstractie en de scheiding van goed gedefinieerde belangen dragen bij tot het beheersen van complexiteit in concurrent software.

De voorgestelde methodologie definieert de volgende ingrediënten:

- 1. Een grafische modelleringstaal definieert grafische notaties en regels die afgeleid zijn van CSP. De grafische modelleringstaal wordt gebruikt voor het specificeren, ontwerpen grafisch en procesarchitecturen. programmeren Dit resulteert van in zogenaamde CSP diagrammen.

- 2. Een *object model* implementeert de CSP concepten door middel van object-georiënteerde technieken. Dit model kan vervolgens worden geïmplementeerd in object-georiënteerde programmeertalen. Dit resulteert in *CSP bibliotheken* voor Java, C (in object-georiënteerde stijl) en C++.

De grafische modelleringstaal en het object model sluiten op elkaar aan. CSP diagrammen worden gebruikt om procesarchitecturen te beschrijven en te analyseren. Een CSP bibliotheek wordt gebruikt om procesarchitecturen te implementeren in een object-georiënteerde programmeertaal. Deze methodologie maakt gebruik van procesgeoriënteerde en object-georiënteerde technieken en verbergt threadgeoriënteerde technieken.

De voorgestelde methodologie is toegepast op regelapplicaties voor ingebedde computer systemen.

# $_{\text{CHAPTER}}1$

## Introduction

# 1.1 Concurrency and complexities in embedded control software

In this thesis, we are concerned with the development of embedded control software for mechatronic systems. Mechatronics deals with controlled mechanical systems that are designed as a whole. Mechatronic design is the integrated design of a mechanical system and its embedded control system. A mechatronic design approach leads to more flexible and cost effective machines with better performance (van Amerongen, 2003). Examples of mechatronic systems are robots, production machines, modern cars, airplanes, CD- and DVD-players, etc. The controller part of a mechatronic system is mostly realized in software as an embedded control system. Embedded control systems require safety, reliability, robustness, and the guarantee that their processes meet their deadlines for a safe and reliable operation of the entire system. Those systems are hard real-time and inherently concurrent since they interact and respond in time to a concurrent world.

The total behaviour of a mechatronic system is described by its physicalsystem dynamics, control laws, and the characteristics of the software and hardware. These artefacts are inherently concurrent in which all components participate and aggregate. Concurrency naturally fulfils a glue-logic between the different artefacts and components in software and hardware. It offers the means to integrate components and take away discontinuities between them. In fact, concurrency offers the tools to manage complexities.

Embedded control software is considered both sophisticated and complex. It has to deal with several sources of complexities in software engineering, such as:

- multithreading,

- interrupt handling,

- exception handling,

- inter-processor communication,

- priority scheduling and preemption,

- precise timing and sampling,

- reactivity and responsiveness,

- safe-guarding and fault-tolerance.

These sources of complexities concern concurrency in both software and hardware. Software design and programming tools, languages, and methods have to deal with these sources of complexities. Commonly, adhoc solutions are offered that deal with these issues. Ad-hoc solutions are individual solutions meant for one thing only. It is up to the user to integrate these ad-hoc solutions into a concurrent framework. This process is being complicated when a paradigm of loosely coupled concepts are used. These ad-hoc solutions require a common level of abstraction in order to understand the separate concerns as a whole and in a systematic way.

Software design and programming tools, languages, and methods must capture a good understanding of concurrency. Concurrency should be driven by coherent and formal concepts and not by ad-hoc solutions. Therefore, the foundation that underlies these tools, languages, and methods must contain coherent concepts that integrate the previously mentioned sources of complexities and abstract away from ad-hoc solutions. The semantics of these concepts must be preserved during the development of embedded systems. In this thesis, a methodology is proposed that captures a good understanding of concurrency as a whole, in a natural and systematic way. A keystone of this methodology is *Communicating Sequential Processes* (CSP) (Hoare, 1985; Roscoe, 1998). CSP is a theory embracing fundamental concepts describing and understanding concurrency in a formal and systematic way. The foundation that underlies the proposed methodology is suitable for developing embedded software, in particular, embedded control software.

## **1.2 Scope of subject**

## **1.2.1 Embedded control**

The following definitions are frequently used in this thesis, which are derived from common definitions found in literature and on the internet.

An *embedded system* is a combination of computer hardware and software that is embedded in a larger system, hidden from the end-user. A common characteristic of an embedded system is that it is programmed to perform a set of functions that minimizes end-user or operator intervention; thus an embedded system automates a product.

A *real-time system* is one in which the correctness of the system depends not only on the logical results, but also on the time at which the results are produced.

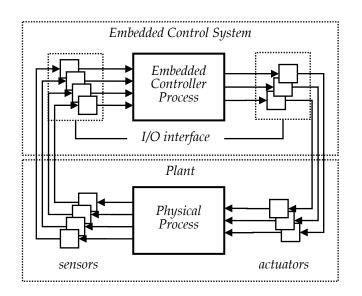

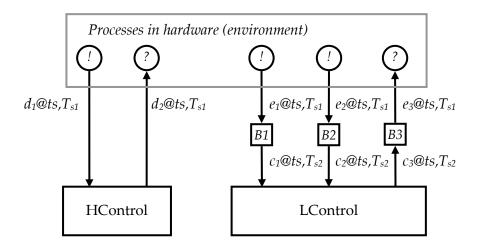

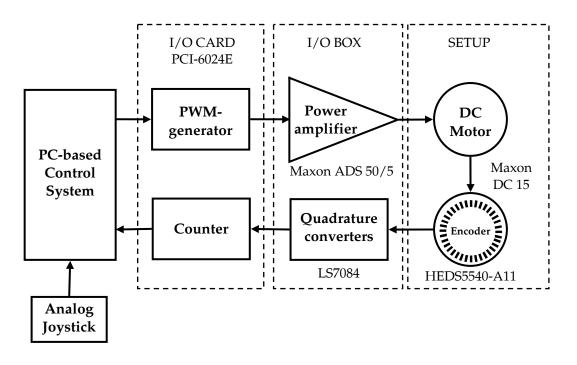

An *embedded control system* is an embedded real-time system with the task of controlling a physical process. An embedded control system consists of one ore more control loops (i.e. controller processes) interacting with a physical process through sensors, actuators and its input/output interface. A blueprint of an embedded control system, as part of a mechatronic system, is depicted in Figure 1-1.

Figure 1-1 Blueprint of a mechatronic system.

A *sensor* is a device that responds to a physical stimulus (heat, light, pressure, motion, flow, and so on), and produces a measurable corresponding electrical signal. This electrical signal is translated by the computer hardware into a digital value that is consumed by the control software.

An *actuator* is a device which performs a physical action to an electrical stimulus generated by the computer hardware.

The electrical circuits that perform signal conversion between the computer, sensors, and actuators are called the *input/output interface* (I/O interface) of the embedded computer system. The arrows between the embedded control system and the plant are usually electrical signals. The arrows between the embedded control system and its I/O interface are digital signals and the arrows between the plant and the sensors or actuators are physical stimuli.

The controller process interacts with one or more physical processes. The behaviour of this control process is composed by at least two parallel processes that engage in communication at discrete moments in time. Conceptually, a controller process is event-driven, which may engage in respectively periodical communication events, sporadic communication events, or perhaps a mix of both. The communication events represent the completion of signal conversion (e.g. sampling and actuation), based on fixed or variable time intervals. In this thesis, hard real-time control systems are considered for which every missed deadline is an error. Therefore, the communication events must happen within a deadline or at precise moments in time. The real-time behaviour of an embedded control system is observable by tracing the events. These traces are suitable to guarantee the proper functioning of the system.

Embedded control systems are often part of larger heterogeneous systems connected by their I/O interfaces. These systems vary from single central processor unit (CPU) systems that are compact and constrained by a limited amount of resources (e.g. memory and CPU speed), to single CPU systems with ample system resources, or to multiple CPU systems distributed over a plant. Considering the variety of concerns in hardware and software and the variety of ad-hoc solutions to these concerns, it is not surprising that embedded software engineering is often considered complex and specialized, even without considering the difficulties of control law design. A programming model is required which deals with this complexity in an elegant way. Such a programming model is usually based on a *real-time kernel* (RTK) technology that provides an abstract layer of services, which controls the hardware and schedules multiple threads of control. This layer comprehends an application programming interface (API) with desirably low overheads. A RTK can exist as a microkernel real-time operating system (RTOS) (e.g. QNX (1998), CMX-RTX (1998) or  $\mu$ C/OS (1998)) or as part of a larger real-time operating system (e.g. Real-Time Linux (FSMLabs, 2002; RTAI, 2002), VxWorks (WindRiver, 2002), and OS9 (RadiSys, 2002)). These RTKs provide loosely coupled imperative primitives (e.g. thread control and synchronization, signal handling, and timed interrupt handling) which widen the number of features but complicate writing reliable concurrent software at the same time. No RTK is the same and their semantics and behaviour are not uniform for real-time systems. One may realize that this programming paradigm is meant to instruct the processor, but this paradigm is too low level and too detailed for the human understanding of the structure and behaviour of control software. Furthermore, the API incorporates ad-hoc solutions to pathological problems, such as deadlock and livelock, and priority inversion. This is done by using respectively asynchronous communication and priority inheritance techniques to cure illnesses in the implementation rather than providing guidelines or rules to prevent them in the first place.

#### 1.2.2 Computer-aided design tools

Computer-aided design (CAD) tools for developing control software, such as the Real Time Interface (RTI) from dSPACE (2002) and the Real Time Labview Module (RTLM) from National Instruments (2004), are world-widely known and used for creating control software. These tools deliver a powerful graphical development environment for signal acquisition, measurement analysis, data presentation, and model-based control system design. Essentially, they give the flexibility of a language the complexity programming without of traditional development tools and give all-in-one solutions for dedicated hardware. Their success is due to the automation of code generation and system monitoring, which negates the need for the control engineer to code. The tools are guided with documentation and are easy of use.

Under the hood of RTI and RTLM, these tools hide a rigid software framework that is performed by the embedded computer system. The core of the generated code is basically a simulator that comprises a sequential state machine, which is timed on constant timing intervals. This sequencing makes model checking for tracing pathological problems unnecessary, but the sequential framework becomes complicated when unavoidable. Concurrency involves concurrency is performing distributed tasks in parallel, triggering tasks at a specified time interval, and assigning equal or different priorities to each parallel task. This is specified in a process diagram, apart from block diagrams that describe the functionality of the controller. A process diagram specifies the tasks (specified by block diagrams) to be performed in parallel or on (timed) interrupts. Once the block diagrams and process diagram have been completed, the controller is up and running on the processor board by a few user actions.

Despite the flexibility and user-friendliness of these CAD tools, the concurrency paradigm that is used in the translation from a process diagram to its implementation is based on RTOS or RTK primitives. The semantics of these primitives may not be uniform and these primitives complicate the code. The automation from design to code, results in a one-way transformation disallowing round-trip engineering. Consequently, customizing the framework for an initially unsupported computer target is a costly task that is dedicated for specialists.

A concurrency paradigm should have been used that scales well with complexity, is highly portable, and that is uniform. CSP offers a concurrency paradigm that fulfils these requirements. CSP provides a good foundation for CAD tools to develop control software. Examples of which can be found in THESIS (1993) and Ptolemy II (2003). These methods describe two different control software design strategies. These strategies benefit from using CSP for building concurrent control software in an elegant way. THESIS and Ptolemy use simplified CSP constructs, which are restricted for a broader use.

## 1.2.3 Multithreading

Concurrent software involves multithreading. Multithreading is the ability to have more than one task occurring in a program (Lewis and Berg, 1996; Silberschatz and Galvin, 1994). A *thread* is a set of statements or coherent functions that execute sequentially at the same priority. Multithreading improves the utilization of a single or multiple CPUs, whereby the program can continue performing those tasks that are not waiting for an event to happen. This improves the throughput and responsiveness of the program.

A scheduler slices the main thread for each available CPU into multiple sub-threads (semi parallel). A thread is scheduled on a CPU and comprises a program context; i.e. the program counter, general registers, stack pointer, and the stack. At any one time only a single thread can be executed on a CPU. A multiprocessor system with n CPUs can therefore

execute *n* threads simultaneously (truly parallel). The entirety of a (sub-) thread is also known as a task.

Synchronization is required between multiple threads upon a shared resource. Two important synchronization primitives are semaphores (Dijkstra, 1968a) and monitors (Brinch-Hansen, 1973; Hoare, 1974). Both synchronization primitives offer various kinds of mutual exclusion constructs (or critical regions), where each thread may enter the construct (or region) one at the time. Hoare (1974) described a fair monitor as a concept for operating systems based on Dijkstra's semaphores. Derived monitor implementations are found in modern operating systems and in programming languages like Java (Arnold et al., 2000) and C# (Microsoft, 2003).

These synchronization constructs may depend on global conditions among different synchronization constructs. However, these synchronization constructs cause a few problems:

- The synchronization primitives intertwine with objects, which complicate the implementation of the objects. While the software grows, its complexity may not linearly scale with the growth. Consequently, the understanding and the verification of its correctness will become error-prone and hard to grasp.

- In case the synchronized resource is an object that mostly is accessed by a single thread, the synchronization construct decreases the overall performance.

Operating systems offer higher-level constructs that encapsulate semaphore and monitor constructs. Examples of such higher-level constructs are signal-handling, mailboxes, input/output-streams, and barriers (joins). The higher-level constructs make concurrent software less error-prone and they are applied when multiple threads are certainly involved. We observe these higher-level constructs as ad-hoc solutions to individual problems without collaborating to coherent concepts and without a formal mathematical foundation.

Hoare advocates reasoning about concurrency with processes and events, rather than with threads and monitors (Hoare, 1985). Monitors

are too complicated to understand the behaviour of a complex concurrent program. Instead, Hoare developed CSP as a formal foundation for describing concurrent systems. CSP is also multithreaded but it surpasses threads, semaphores, and monitors by defining channels and other related fundamental primitives. CSP provides all the syntactic and semantic information for describing and understanding concurrency based on fundamental and compositional semantics. CSP is further discussed in Section 1.4.3.

### 1.2.4 Occam and Transputer

The transputer and occam technology provided a simple and elegant platform for building sophisticated, reliable and robust control systems. The parallel programming language occam (Inmos, 1988) is an implementation of a subset contained in CSP. Furthermore, occam is a highly secure programming language, which detects hazardous or errors-prone concurrency constructs at compile-time. Transputers are microprocessors that are designed to execute occam programs most efficiently. Transputers are equipped with four links. Transputers are building-blocks in homogeneous multiprocessor systems based on distributed memory. A *link* is a peer-to-peer connection between transputers that provides external channel communication between processes distributed on a network of transputers.

The manufacturing of transputers ceased around 1996. Ivimey-Cook (1999) notes that the Inmos transputer was more than a family of processor chips, it was a concept, a new way of looking at system design problems. In many ways, that concept lives on in the hardware design houses of today, using macro cells and programmable logic. STMicroelectronics continues with the transputers core of the T414, in a low-cost chip called the ST-20, which is no longer referred to as a transputer. The ST-20 is nowadays sold as the STi5518 CPU which can be found in many TV set-top boxes and satellite receivers. Transputer links are found in other products. DEC's Alpha processor 21364 uses transputer-class links for building multiprocessor configurations (DEC,

2003). Transputer-class links are used for SpaceWire networks for the space industry (4Links, 2003; SpaceWire, 2003).

Since transputers, as such, have become obsolete, the programming language occam evolves slowly and is still supported by a small community in the world. Translators exist for porting programs that are written in occam to processors other than transputers. Two translators are available: Kent Retargetable Occam Compiler KROC (KROC, 1999) and the Southampton Portable occam Compiler SPoC (SPoC, 1998). KROC translates transputer code that is produced by the occam compiler to native code for a target processor and SPoC translates transputer code to portable C code. Recently, the occam compiler source code has been released. An updated occam compiler supporting an updated occam programming language may be expected in the future. Despite these efforts, the future of occam is very uncertain. Occam suffers from not being a popular programming language due to the fact that the concepts behind occam are not well known by most software developers and perhaps the syntax is not favoured among programmers. The programming languages Ada (Barnes, 1988), Limbo (Stanley-Marbell, 2003), and Handel-C (Page, 2001) have similar roots. Similar to the aforementioned reasons, Ada and Limbo also suffer from lack of worldwide acceptance. However, Handel-C is C-alike and grows in popularity for programming field programmable gate arrays (FPGA). On the other hand, the look-a-like syntaxes of C (Kernigham and Ritchie, 1988), C++ (Stroustrup, 2000) and Java are preferred and widely accepted. One can imagine that the C, C++ and Java community could benefit from CSP by providing a CSP library for these programming languages. Furthermore, such a CSP library should be suitable for heterogenous multiprocessor systems based on shared or distributed memory

### **1.2.5 THESIS**

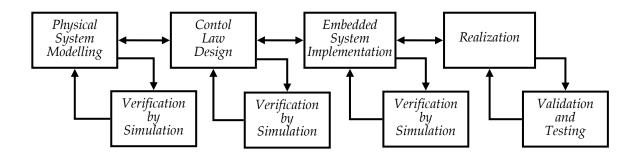

A sound and intuitive foundation for the realization of control software and hardware was described by Wijbrans (1993). This resulted in the *Twente Hierarchical Embedded Systems Implementation by Simulation* (THESIS) method, which investigated the use of parallel processing and structured design methods for embedded control system realization. This method was aimed at filling the gap between the derivation of the control algorithms and the controller realization by recommending a strategy that guides the engineer during the design process, provides a formalism for the description of the controller, and suggests support tools that aids the engineer during the design process.

A control application is inherently data-flow oriented. Therefore, THESIS was naturally based on a channel-based methodology in order to guarantee consistencies and filling the gap between the different stages in the controller design and the final code. Wijbrans chose a software design tool based on the structured analysis and structured design (SA/SD) method of Hatley and Pirbhai (1987). The implementation and realization of the design is based on the parallel programming language occam and transputer hardware. Due to the CSP concepts that come with occam and transputers, this method resulted in reliable, robust, and wellstructured real-time control software for various mechatronic systems at the laboratory of Control Engineering. THESIS was applied to several industrial applications (Wijbrans, 1993). The technical abstraction that with and transputers reduced comes occam complexities in implementing controller software. This increased the development speed imperative programming, which to uses sequential compared programming languages, like C or C++, with multithreading primitives. This is an important lesson we learn from occam and transputers.

The Hatley and Pirbhai method, occam, and transputers are considered outdated, taking into account the present trends in technology. These should be replaced by technology that keeps THESIS up-to-date.

## 1.3 Aim of research

Considering the scope of subject, the aim of this research is formulated as follows:

The aim of this research is developing a CSP-based methodology for building embedded real-time software for heterogeneous embedded control systems.

This aim is multilateral because concurrency concerns all phases of software engineering. For each phase a sub-aim can be formulated:

- In the *specification phase* this research aims at identifying and specifying concurrency as part of the requirements.

- In the *design phase* this research aims at designing solutions to the problems, while maintaining concurrency and dealing with complexity reduction and absorption.

- In the *implementation phase* this research aims at the development of an object-oriented concurrent framework that protects the engineer from needing exclusive skills on programming threads.

- In the *realization phase* this research aims at porting the implementation to hardware so that the hardware is efficiently used and satisfies the required performance.

- The concurrent software should be systematically tested to determine whether or not the software satisfies the required specification.

The methodology should deal with common sources of complexities in programming concurrent software, such as multithreading, interrupt handling, exception handling, inter-processor communication, priority scheduling, reactivity, responsiveness, etc. These technical issues should be elevated to a high level of abstraction in order to simplify the design of the application and to simplify the required mindset of the engineer. The resulting concurrent software should be similar to that obtained by an experienced software engineer. A structured approach using sound and proven concepts is required, which deals with these technical issues without introducing surprises, discontinuities, or non-scalable complexities. Such a structured approach should stretch over all phases of software engineering. The approach should provide an architectural view that binds all phases in the development process and can be implemented when completeness is achieved. The continuity and consistency between the different phases of software engineering should be guaranteed, which allows for rapid prototyping and round-trip engineering. The proposed methodology should provide the technical "how to's" for building concurrent software.

The proposed methodology is guided by the following goals:

- to make things reasonably safe but not too restrictive,

- to make compromises so as not to introduce unreasonable inefficiencies,

- applicable for real-time and embedded applications, in particular for control applications,

- and portable among different platforms.

It is expected, due to experiences with occam, that the CSP concepts will result in tools that obtain control software at a fast pace in development and at a moderate cost. The programming languages C, C++, and Java are of interest for coding control software since these programming languages are used and supported by the vast majority of embedded software engineering companies. The proposed methodology will be applied to several embedded control systems. During this research 20-sim (2003) is used for controller design and automatic code generation of the control laws.

## 1.4 Research approach

## 1.4.1 Complexity

The growth of software, in terms of size and the number of features it should perform, increases the complexity of software. The software engineer must deal with this complexity. Software design tools, modelling and programming languages, and software design methods are slowly evolving in order to simplify this task. However, the lack of common concepts that stretches over these tools, languages, and methods cause discontinuities between them. These discontinuities are hurdles in the software design trajectory. The solution to this problem is to eliminate discontinuities between the different models and phases in the software design trajectory. In order to understand what is required, we elaborate on complexity in this section.

Complexity is a conception that is related to the human intuition. One person may find something complex to understand whereas someone else may find it simple to understand. In order to understand this phenomenon of complexity, complexity is defined as follows:

**Definition (complexity):** *Complexity* is the amount of thought it takes a person to grasp a problem and/or to develop a solution to that problem.

The amount of thought depends on many factors which are human related, i.e. previous knowledge and the ability of complexity reduction (simplification through abstraction, generalization, or mental images) and complexity absorption (speed and capacity of remembering, followed by reconstruction). Complexity is something that is cognitive or subjective and can be different for each individual person or common to a group of persons who share similar skills. Complexity can be measured by comparison between two or more alternatives. Quantities have been proposed to measure complexity and capture all our intuitive ideas about what is meant by complexity and by its opposite, simplicity. Complexity is often measured by time measures or information measures (Gell-Mann, 1995). Time measures express how much time or steps it takes to grasp the problem or to finish a computation. Information measures express the length of the shortest message conveying certain information. Complexity measures are context-dependent.

In order to manage complexity, a common context-related language is required, which the human mind can easily grasp with assumed previous knowledge and understanding. The language should advocate complexity reduction and complexity absorption, which eventually results in reasonably low complexity measures. Time measures and information measures are reduced by concurrency. In other words, concurrency manages complexity! Therefore, the language should incorporate concurrency. Most tools, languages, and methods lack a good understanding of concurrency and not surprisingly they fail to describe a concurrent system with low complexity measures. The UML is a good example of a common language that suffers from discontinuities between different diagrams (or views), due to a poor concurrency model. Its concurrency concepts do not stretch over the multiple views and this makes concurrent software complex and error-prone rather than simpler and safe. Apparently, a wrong concurrency paradigm has been used in the UML.

A mathematical foundation may contribute to a quality of understanding and reasoning about the behaviour of concurrent software. Often the results of mathematics can be summarized to formal and abstract concepts, implemented as practical constructs, guidelines, and rules. This is similar for CSP and its underlying theory. CSP comprehends a mathematical foundation, whereby simplification is achieved due to abstraction and a separation of well-defined concerns.

## 1.4.2 Concurrency

We live in a concurrent world where multiple tasks exist at the same time. These tasks are carried out in parallel, in sequence, or by some choice, and possibly communicate with each other. As in real life, clarity is obtained through concurrency. If one had to describe the behaviour of our environment as a strictly sequential model (or as one task) then this would be too complex. Concurrent tasks exist at the same time, and they can be observed individually or in composition of other tasks. The existence of multiple tasks at the same time does not imply that these tasks are in parallel. Some tasks may be in parallel, some are waiting for another task to complete, or tasks are alternatively performed due to certain conditions. Parallelism implies that when a task has to wait for an event to happen, another task can continue. This most likely increases the overall throughput and responsiveness of an application.

Although the high performance and the simplicity of a computer is attributed to concurrent hardware, concurrency in software is often thought to be an advanced topic that is much harder than serial computing.

The term *concurrent* is often used as a synonym for *parallel*. These terms have something in common but their nature has different semantics. Essentially, concurrency comprehends more than just parallelism. For example, consider a simple system of two communicating computers in parallel. The parallelism is simply and solely not sufficient for understanding the behaviour of the system. More interesting still, is the understanding of the total behaviour of the system as an aggregation of sequential parts on each of the two computers, which are executed in parallel and that synchronize on communication. The elements sequential, parallel, synchronization, and communication are subject to concurrency in the system. Such a system is known as a *concurrent system*, where there is more than one process existing at a time, whose component processes interact with each other by communication. Concurrency accommodates common goals, whereas parallelism accommodates two or more independent goals with respect to performance requirements. The distinction between concurrency and parallelism helps a great deal in separating concerns in embedded system engineering. In this thesis, the term concurrent system is used when the parallel system is viewed as a whole and the term parallel system is used when the distribution of individual computers in the system is considered.

Concurrency is defined as follows:

**Definition (concurrency):** *Concurrency* is an abstraction of behaviour, where the system is viewed as a set of parallel, sequential, and alternative processes that interact with each other by communication.

In sequential programs, parallelism is replaced by sequential patterns of code which sequence is valid in parallel form. In a sequential language, communication is a combination of actions on shared variables or shared objects, whose actions are streamlined by a single sequential flow of control. In this sense, concurrency in sequential programs is done implicitly. Roscoe (1998) points out that this happens too implicitly in sequential programming languages. This becomes a major disadvantage when using a sequential programming language for creating concurrent (multithreaded) programs. Roscoe brings to mind that "this effect also shows up when it comes to mathematical reasoning about system behaviour: when it is not made explicit in a program's semantics when it receives communications, one has to allow for the effects of any communication at any *time."*. A paradigm that comes from true parallel systems (e.g. computer hardware, electronic components, etc.) benefits from concurrency and makes systems simpler. This illustrates that concurrency is too powerful and, indeed, too simple an idea to be set aside. With a better handle, it can simplify both the design and the implementation of most complex systems, as well as boost performance.

Concurrency should provide:

- a powerful tool for *simplifying* the description of systems;

- natural separation of concerns at the highest level of abstraction in terms of processes and their interrelationships;

- performance that spins out from the above, but is not the primary focus;

- a model that is mathematically, clean springs no engineering surprises, and scales well with system complexity.

The observable and fundamental entities of concurrent systems are events. An *event* is an occurrence in time and space, which involves two

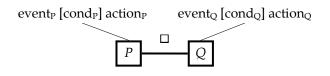

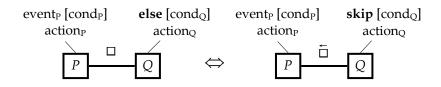

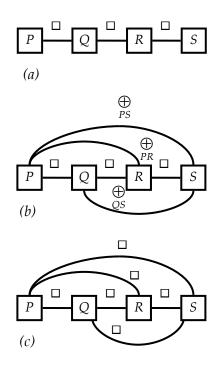

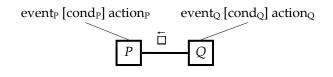

or more processes that engage in the event. One process cannot engage in an event on its own. During the event, particular indivisible actions are performed. These actions are strictly concurrency related, such as, data transfer, synchronization, and thread scheduling. An event represents the completion or successful termination of its actions, which only occurs when all associated processes rendezvous with each other. An event is *not* an object, it is not simply a method call on an object, and it is not an expression that becomes true. An event can only occur on rendezvous between two or more processes. The term *process* will be explained in Section 2.3.1.

In this thesis, we distinguish between communication events, timeout events, termination events, and exception events. А communication event is the occurrence of two processes engaged in communication over a channel or barrier. A termination event is the transition from one process to a subsequent process. A *timeout event* is a rejection of communication when it is not ready before a specified time. An *exception event* is an internal event of a process that stops the process from making progress. Communication events and termination events are the primary events from which timeout events and exception events are derived.

### **1.4.3 Communicating Sequential Processes**

CSP is a theory of programming and a notation for describing concurrent systems whose component processes interact with each other by communication (Hoare, 1985; Roscoe, 1998). Its concepts are based on mathematics and compositional semantics. In CSP, one can specify requirements precisely and prove that they are satisfied by our implementations. CSP is about 10 years newer than object-orientation and 5 years newer than monitors. The theory has evolved over time and its concepts are timeless (Hoare, 1978; Hoare, 1985; Roscoe, 1998; Schneider, 2000).

CSP deals with processes, networks of processes and various forms of synchronization and communication between them. A network of

processes is also a process and so CSP naturally accommodates layered (or nested) structures, i.e. networks of networks. A CSP process isolates data and operations from other processes. Its behaviour is completely described by the way it communicates with its external environment via *channels*. A channel performs a barrier synchronization between two processes. A *barrier* is a rendezvous point on which two or more associated processes are blocked until all processes reach the rendezvous point. A barrier can be represented by a single channel between two processes, by a bundle of channels between two or more processes, or by a parallel construct that terminates when all participating processes have terminated. Channel and barrier communication are observable as communication events.

Processes are components that are complete and have no complex dependencies on other components. The definition of a process comprises syntactic and semantic information on how the process interacts with its environment. This information is entirely specified through a defined interface—its abstraction—consisting of various synchronization primitives as defined in CSP. The synchronization primitives encapsulate the principles of multithreading and brings about channels, barriers, and binary operators. These binary operators are represented as compositional constructs.

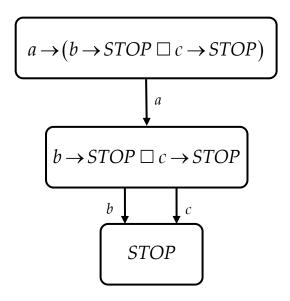

CSP is founded on what is called *compositional semantics*. CSP offers three distinct ways of describing the meaning of a program, namely operational, denotational, and algebraic semantics. The operational semantics interprets programs as state diagrams. The denotational semantics maps a language into an abstract model in such a way that the value (in the model) of any component is determinable directly from the values of its immediate sub-components. These values are based on traces, failures, and divergences (Roscoe, 1998). Algebraic semantics are defined by a set of algebraic laws. Each semantic complements each other. The mathematics are left to the CSP books (Roscoe, 1998; Schneider, 2000) and model checking tools (FDR, 2004; ProBE, 2003), but its assets should be brought to practical use for the user to describe the compositional semantics of the software suitable for formal analysis.

### 1.4.4 Strategy

A concept is an abstract principle with a well-defined semantics. A concept is less sensitive to changes than its implementation. After all, good concepts live longer than their implementations. Concepts are the building-blocks of a methodology. Therefore, the quest of this research is to develop an implementation using modern technology that replaces occam and transputers while maintaining the invaluable CSP concepts. The implementation of the CSP concepts is the foundation for the proposed methodology.

The aim of this thesis is accomplished by realizing the following goals:

- 1. A CSP-based graphical modelling language should be defined for specifying and designing control architectures using graphical notations.

- 2. A object model should be developed that implements the CSP concepts using object-oriented techniques. The object model should be abstract, but eventually the model must be implemented in the programming languages C, C++, and Java. This should result in three CSP libraries for C, C++ and Java. Currently, the Java run-time environment takes significant run-time overhead, making it unsuitable for embedded real-time systems. Therefore, the CSP libraries for C and C++ are meant to boost performance on embedded systems.

- 3. Demonstrate the proposed methodology on several control systems at the laboratory of Control Engineering.

The object model is prototyped in Java and partly documented using UML diagrams. Java was used for the following reasons:

- Java is popular and world-widely supported,

- Java is better than C++ (i.e. simpler, safer, C look-a-like),

- Java was meant for embedded systems,

- Java is object-oriented and multithreading is supported within the language and the Java run-time system.

The prototype in Java was meant for educational purposes and from which C and C++ versions should be derived. A version in C and C++ is required in order to boost performance. UML diagrams are used to document the object model.

Valuable aspects of component-, process-, and object-oriented technologies should be incorporated in the object model. A relationship with other methodologies, being suitable for creating control software, should be maintained. Methodologies of interest are UML (1998), ROOM (aka RT-UML) (Selic et al., 1994), Octopus (UML version) (Awad et al., 2002), Ptolemy II (Ptolemy, 2003), and structured methods (Hatley and Pribhai, 1987; Yourdon, 1989), and THESIS (Wijbrans, 1993).

## **1.5 Overview of thesis**

The realization of the postulated aims is described in the following chapters:

#### Chapter 2

A structured approach to embedded control systems implementation is discussed. This chapter emphasizes the importance of processes and events during the development of control models and control software.

#### Chapter 3

A graphical modelling language for specifying and designing process architectures is described. The graphical notations are derived from CSP which allow the user to convert data-flow oriented control models into executable models, called CSP diagrams.

#### Chapter 4

A CSP library for Java is described. This library renders the application programming interface (API) of the object model in Java. Also, the library stands model for implementations in other object-oriented programming languages. CSP diagrams can be straightforwardly implemented with this CSP library to Java. The implementation of the API is not described in this chapter.

#### Chapter 5

Real-time behaviour is important and usually priorities are the solution to allow real-time processes to meet their deadlines. A notion of priorities for CSP-based software is described. Priorities are supported by CSP diagrams (discussed in Chapter 3) and are implemented in the CSP libraries for Java and C++ (discussed in Chapter 4 and 6).

#### Chapter 6

The CSP diagrams and the CSP library for C++ have been applied to several embedded control systems. Several applications illustrate how CSP diagrams and the CSP library for C++ contribute to the development of reliable and robust control software.

#### Chapter 7

The results of this research are reviewed. Conclusions and recommendations are subject of this chapter.

# CHAPTER 2

## A Structured Approach to Embedded Control Systems Implementation

## **2.1 Introduction**

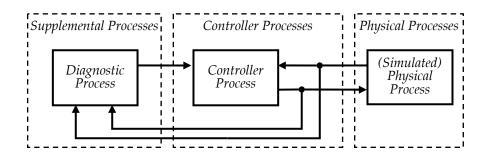

Control systems are concurrent systems, which involve processes deployed in hardware and in software. These processes perform tasks at periodic intervals (e.g. sampling, actuation, and data processing) or at sporadic stimuli from the environment (e.g. mode-switching, safeguarding). These processes must guarantee real-time constraints; e.g. reactivity, responsiveness, and deadlines. The control software integrates concurrency related concerns, such as multithreading, interrupt handling, exception handling, timing, and scheduling. These concerns propagate through the design and implementation of control applications for which an appropriate understanding of concurrency is crucial to their development.

The above mentioned concurrency related concerns can complicate the implementation of the execution framework when these concerns are treated as ad-hoc solutions. The transformation of the controller design to its implementation is usually automated, which hides the complicated code framework from the user. Consequently, the user has control over the objects in the design, but the user has restricted control over the execution framework and its performance. This automation is not a problem unless its restrictions become a burden. This can cause a serious

gap between a controller design and its implementation on dedicated target platforms. A structures approach is required that is based on sound and formal concepts that enable the integration of concurrency related concerns without surprises.

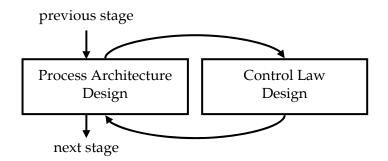

The user is primarily focussed on processes during the design of a control system, and secondarily on objects. A control system is a process of one or more control loops. Each control loop is a process that is performed partly in software and partly in hardware. The control engineer is concerned with a hierarchy of processes during specification, design, implementation, and verification by simulation of control system. It are those processes that describe the behaviour of the system. Processes and objects go hand in hand, whereby objects implement processes. Therefore, a control system is not solely described in terms of objects, as some object-oriented engineering approaches do suggest. The THESIS method (Wijbrans, 1993) showed that process-orientation offers a structured approach to control system design and implementation. Although THESIS is more than 10 years old, most of its propositions are still applicable to the methodology presented here.